### AFF3CT Runtime × julia – New Features & Roadmap

$2^{\rm nd}$  AFF3CT User Day

Adrien Cassagne<sup>†</sup>, Maxime Millet<sup>†</sup>, Julien Sopena<sup>†</sup> and Alix Munier<sup>†</sup>

<sup>†</sup>Sorbonne University, LIP6, CNRS, Paris, France

November 28, 2023

### Table of Contents

$\blacktriangleright$  Introduction

▶ New Features

▶ Roadmap

$\blacktriangleright$  Conclusion

# Remainder of Previous AFF3CT User Days

• AFF3CT split into 3 open source projects (MIT license)

- AFF3CT<sup>1</sup>: Library & simulator for error correcting codes

$\circ~$  GitHub: 426  $\bigstar$  – 135 forks – 90k lines of code

- AFF3CT-core<sup>2</sup>: Dataflow DSEL & multi-threaded runtime

$\circ~$  GitHub: 1  $\bigstar$  – 2 forks – 20k lines of code

- MIPP<sup>3</sup>: Portability & expressiveness for CPU SIMD instructions

- $\circ~$  GitHub: 440  $\bigstar$  85 forks 30k lines of code

<sup>1</sup>A. Cassagne, O. Hartmann, M. Léonardon, K. He, C. Leroux, R. Tajan, O. Aumage, D. Barthou, T. Tonnellier, V. Pignoly, B. Le Gal, and C. Jégo. "AFF3CT: A Fast Forward Error Correction Toolbox!" In: *Elsevier SoftwareX* 10 (Oct. 2019), p. 100345. DOI: 10.1016/j.softx.2019.100345.

<sup>2</sup>A. Cassagne, R. Tajan, O. Aumage, D. Barthou, C. Leroux, and C. Jégo. "A DSEL for High Throughput and Low Latency Software-Defined Radio on Multicore CPUs". In: *Wiley Concurrency and Computation: Practice* and Experience (CCPE) 35.23 (July 2023), e7820. DOI: 10.1002/cpe.7820.

<sup>3</sup>A. Cassagne, O. Aumage, D. Barthou, C. Leroux, and C. Jégo. "MIPP: A Portable C++ SIMD Wrapper and its use for Error Correction Coding in 5G Standard". In: *Workshop on Programming Models for SIMD/Vector Processing (WPMVP)*. Vösendorf/Wien, Austria: ACM, Feb. 2018. DOI: 10.1145/3178433.3178435.

## $\underset{^{1} \text{ Introduction}}{\text{Main Purposes of this Talk}}$

1 Give you an overview of the recently introduced features

2 Talk about what is next: special focus on AFF3CT-core and julia

3 Discuss with you about the directions to take

### Table of Contents <sup>2</sup> New Features

▶ Introduction

$\blacktriangleright$  New Features

▶ Roadmap

$\blacktriangleright$  Conclusion

## Single Instruction Multiple Data with MIPP 2 New Features

- MIPP enables

- Efficient implementations

- **Portability** over the most common architectures

- Code  ${\bf readability}$  compared to intrinsic functions

MIPP MIPP!

# $\underset{^{2} \text{ New Features}}{\textbf{Single Instruction Multiple Data with MIPP}}$

- MIPP enables

- Efficient implementations

- **Portability** over the most common architectures

- Code **readability** compared to intrinsic functions

MIPP MIPP!

- New features

- **Unsigned integers** support (relevant for some signal processing algorithms)

- Partial support of SVE

- SVE Length Specific

- Most common operations for floating-point numbers

- $\circ~$  SIMD ISA in ARMv9 and in Fujitsu A64FX CPUs (in Fugaku, the World n°2 Supercomputer)

- Working on a **code generator** (L. DENDANI'S 6 months internship @ IFPEN)

#### Single Instruction Multiple Data with MIPP <sup>2</sup> New Features

- **MIPP** enables

- Efficient implementations

- **Portability** over the most common architectures

- Code **readability** compared to intrinsic functions

MIPP MIPP!

- New features

- **Unsigned integers** support (relevant for some signal processing algorithms)

- Partial support of SVE

- SVE Length Specific

- Most common operations for floating-point numbers

- $\circ~$  SIMD ISA in ARMv9 and in Fujitsu A64FX CPUs (in FUGAKU, the World n°2 Supercomputer)

- Working on a **code generator** (L. DENDANI'S 6 months internship @ IFPEN)

#### • Collaborations

- IFP Energies Nouvelles (IFPEN)

- Inria Bordeaux

- $\circ~$  Open position for a 6 months internship  $\rightarrow$  Code generation, SVE & RVV

# AFF3CT-core for Streaming Applications

"At the creation of the Universe, AFF3CT & AFF3CT-core was a single project."

- **AFF3CT-core has been extracted from AFF3CT** as is it no longer specific to digital communications

- Still, AFF3CT-core is a strong dependency in AFF3CT

- Enable to work in an asynchronous way on both projects

"At the creation of the Universe, AFF3CT & AFF3CT-core was a single project."

- **AFF3CT-core has been extracted from AFF3CT** as is it no longer specific to digital communications

- Still, AFF3CT-core is a strong dependency in AFF3CT

- Enable to work in an asynchronous way on both projects

- A DSEL and a runtime to support a large range of applications

- Digital communications: DVB-S2 transceiver, DVB-RCS2 transceiver, ...

- Computer vision: real-time meteor detection systems

- Post-quantum cryptography: on going work of Andrea LESAVOUREY

- DNN inference: Enrique GALVEZ's 6 months internship starting February'24 (co-supervised with Alix MUNIER @ LIP6)

- → Streaming applications!

**(**

Task

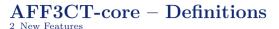

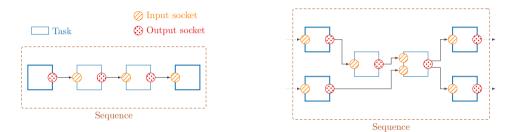

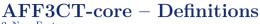

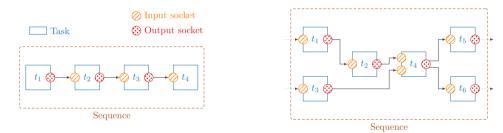

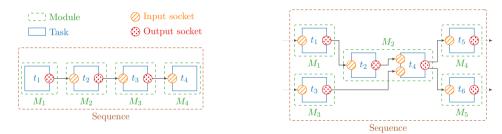

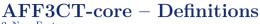

### AFF3CT-core – Definitions

⊘ Input socket ⓒ Output socket

• Directed graphs are supported to map a wide range of apps

### AFF3CT-core – Definitions

- Directed graphs are supported to map a wide range of apps

- A sequence is built from an initial and a final list of tasks

- Directed graphs are supported to map a wide range of apps

- A sequence is built from an initial and a final list of tasks

- Tasks execution order (scheduling) is determined by the user binding

### AFF3CT-core – Definitions

- Directed graphs are supported to map a wide range of apps

- A sequence is built from an initial and a final list of tasks

- Tasks execution order (scheduling) is determined by the user binding

- States are contained in *modules* (= C++ classes)

- Directed graphs are supported to map a wide range of apps

- A sequence is built from an initial and a final list of tasks

- Tasks execution order (scheduling) is determined by the user binding

- **States** are contained in *modules* (= C++ classes)

- One task execution is enough to run dependent tasks (single rate SDF)

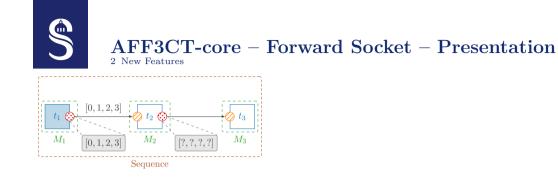

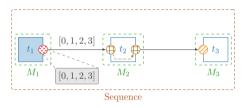

• Data are automatically allocated in the output sockets (see gray rectangles)

- Data are automatically allocated in the output sockets (see gray rectangles)

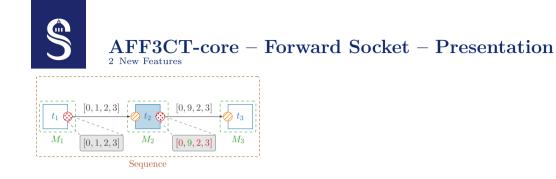

- Let's assume that  $t_2$  only modify the second value of its input socket

- Data are automatically allocated in the output sockets (see gray rectangles)

- Let's assume that  $t_2$  only modify the second value of its input socket

- "0", "2" and "3" are copied into  $t_2$ output socket and "9" value replaces "1"

- Data are automatically allocated in the output sockets (see gray rectangles)

- Let's assume that  $t_2$  only modify the second value of its input socket

- "0", "2" and "3" are copied into  $t_2$ output socket and "9" value replaces "1"

- This is highly inefficient!

- Data are automatically allocated in the output sockets (see gray rectangles)

- Let's assume that  $t_2$  only modify the second value of its input socket

- "0", "2" and "3" are copied into  $t_2$ output socket and "9" value replaces "1"

- This is highly inefficient!

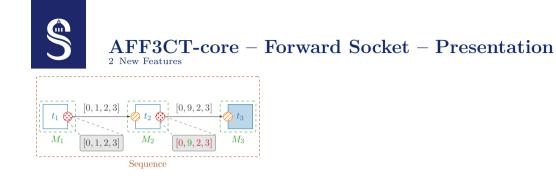

Forward socket: at the same time an input and output socket (read+write)

— There is NO data allocation

- Data are automatically allocated in the output sockets (see gray rectangles)

- Let's assume that  $t_2$  only modify the second value of its input socket

- "0", "2" and "3" are copied into  $t_2$ output socket and "9" value replaces "1"

- This is highly inefficient!

- Forward socket: at the same time an input and output socket (read+write)

— There is NO data allocation

- We propose a new implementation of  $t_2$  with a forward socket

- Data are automatically allocated in the output sockets (see gray rectangles)

- Let's assume that  $t_2$  only modify the second value of its input socket

- "0", "2" and "3" are copied into  $t_2$ output socket and "9" value replaces "1"

- This is highly inefficient!

- Forward socket: at the same time an input and output socket (read+write)

— There is NO data allocation

- We propose a new implementation of  $t_2$  with a forward socket

- $t_1$  output socket is modified in-place ("1" becomes "9")

- Data are automatically allocated in the output sockets (see gray rectangles)

- Let's assume that  $t_2$  only modify the second value of its input socket

- "0", "2" and "3" are copied into  $t_2$ output socket and "9" value replaces "1"

- This is highly inefficient!

- Forward socket: at the same time an input and output socket (read+write)

— There is NO data allocation

- We propose a new implementation of  $t_2$  with a forward socket

- $t_1$  output socket is modified in-place ("1" becomes "9")

- This is efficient and cache-friendly!

# $\underset{^{2} \text{ New Features}}{\textbf{AFF3CT-core}-Forward Socket}-Summary$

- New concept recently added to AFF3CT-core

- Master 1 project with two students (Yacine IDOUAR & Nourdinne HAMMACHI)

- Yacine IDOUAR's Master 1 internship (June to July'23)

- Co-supervised with Julien SOPENA @  ${\rm LIP6}$

- Operate in parallel contexts across pipeline stages & sequence replications

- Continuous integration over extensive unitary testing & documentation

- **Proven to work** on a "real project":  $\times 2$  speedup for meteor detection

## AFF3CT-core – Control Flow & Pipeline

#### • Dynamic control flow

- Not common in dataflow DSL

- Also known as  $feedback\ loop$

- Still, in the DSEL it is more generic as dynamic conditions and switch-cases are also supported

#### — Useful in many cases

- Digital communications: turbo demodulation

- $\circ~$  Computer vision: iterative optical flow

- DNN: feedback graphs

- And so on

#### — Avoid unnecessary unrolling

• Can be seen as a compression

#### — Enable dynamic early exit

- $\circ$  New optimization opportunities

- $\circ \ \ {\bf Static \ graph \ but \ dynamic \ path}$

### AFF3CT-core – Control Flow & Pipeline

#### • Dynamic control flow

- Not common in data flow DSL

- Also known as  $feedback\ loop$

- Still, in the DSEL it is more generic as **dynamic conditions and switch-cases** are also supported

#### -- Useful in many cases

- Digital communications: turbo demodulation

- $\circ~$  Computer vision: iterative optical flow

- DNN: feedback graphs

- And so on

- Avoid unnecessary unrolling

- Can be seen as a compression

#### — Enable dynamic early exit

- $\circ \ \ \, {\rm New \ optimization \ opportunities}$

- Static graph but dynamic path

#### • New features

#### — Control flow inside a pipeline stage

- Tested in continuous integration of comprehensive cases

- Documented

#### — Improved error management

- $\circ~$  Control flow must be within a stage

- $\circ~$  Error message if the data binding is wrong

- Master 1 internship (2 months)

- Nourdinne Hammachi

- $\circ~$  Co-supervised with Julien Sopena @ LIP6 ~

- Still some **limitations**

- A pipeline stage cannot start or end with a Switcher task (select or commute)

- relay task can overcome this issue

- $\circ~$  At the cost of a useless copy...

#### • 2D socket

- Memory is still allocated in a **contiguous way**

- But an additional row buffer is allocated for the  $2^{nd}$  dimension in the socket

- Addressed in the previous buffer need to be recomputed each time a task is triggered

- 3D socket is considered in the future

```

Stateless foo(): // create a module

Task &t = foo.create_tsk("bar"); // create a task

// create a 2D socket (8 rows and 8 cols = 61 elmts)

3

size t si = foo.create_2d_sck_in<int>(t, "in", 8, 8);

// code to execute when the 'bar' task is called

foo.create codelet(t, [si](Module &m, Task &tsk) {

// get a input 2D data pointer

const int** img =

8

9

tsk[si].get 2d dataptr<const int>():

volatile int sum = 0:

for (size t y = 0; y < 8; y++)

11

for (size t x = 0: x < 8: x++)

12

13

sum += img[v][x];

14

return status t::SUCCESS:

15

· ):

```

#### • 2D socket

- Memory is still allocated in a **contiguous way**

- But an additional row buffer is allocated for the  $2^{nd}$  dimension in the socket

- Addressed in the previous buffer need to be recomputed each time a task is triggered

- 3D socket is considered in the future

#### • Task to task binding

- Allow to specify dependencies between tasks more precisely

- Required in some cases

- Non-explicit dependencies (= not described through sockets binding)

- $\circ~$  Forward socket can change the data of an output socket  $\Rightarrow$  the execution order can modify final result

Stateless foo(): // create a module Task &t = foo.create\_tsk("bar"); // create a task // create a 2D socket (8 rows and 8 cols = 61 elmts) 3 size t si = foo.create\_2d\_sck\_in<int>(t, "in", 8, 8); // code to execute when the 'bar' task is called foo.create codelet(t, [si](Module &m, Task &tsk) { // get a input 2D data pointer const int\*\* img = 8 tsk[si].get 2d dataptr<const int>(): volatile int sum = 0: for (size t y = 0; y < 8; y++) 11 for (size t x = 0; x < 8; x++) 12 13 sum += img[v][x];14 return status t::SUCCESS: 15 · ):

#### • 2D socket

- Memory is still allocated in a **contiguous way**

- But an additional row buffer is allocated for the  $2^{nd}$  dimension in the socket

- Addressed in the previous buffer need to be recomputed each time a task is triggered

- 3D socket is considered in the future

#### • Task to task binding

- Allow to specify dependencies between tasks more precisely

- Required in some cases

- Non-explicit dependencies (= not described through sockets binding)

- $\circ~$  Forward socket can change the data of an output socket  $\Rightarrow$  the execution order can modify final result

Stateless foo(): // create a module Task &t = foo.create\_tsk("bar"); // create a task // create a 2D socket (8 rows and 8 cols = 61 elmts) 3 size t si = foo.create\_2d\_sck\_in<int>(t, "in", 8, 8); // code to execute when the 'bar' task is called foo.create codelet(t, [si](Module &m, Task &tsk) { // get a input 2D data pointer const int\*\* img = 8 tsk[si].get 2d dataptr<const int>(): volatile int sum = 0: for (size t y = 0; y < 8; y++) 11 for (size t x = 0; x < 8; x++) 12 13 sum += img[v][x];14 return status t::SUCCESS: 15 · ):

#### • 2D socket

- Memory is still allocated in a **contiguous way**

- But an additional row buffer is allocated for the  $2^{nd}$  dimension in the socket

- Addressed in the previous buffer need to be recomputed each time a task is triggered

- 3D socket is considered in the future

#### • Task to task binding

- Allow to specify dependencies between tasks more precisely

- Required in some cases

- Non-explicit dependencies (= not described through sockets binding)

- $\circ~$  Forward socket can change the data of an output socket  $\Rightarrow$  the execution order can modify final result

Stateless foo(): // create a module Task &t = foo.create\_tsk("bar"); // create a task // create a 2D socket (8 rows and 8 cols = 61 elmts) 3 size t si = foo.create\_2d\_sck\_in<int>(t, "in", 8, 8); // code to execute when the 'bar' task is called foo.create codelet(t, [si](Module &m, Task &tsk) { // get a input 2D data pointer const int\*\* img = 8 tsk[si].get 2d dataptr<const int>(): volatile int sum = 0: for (size t y = 0; y < 8; y++) for (size t x = 0; x < 8; x++) 12 13 sum += img[v][x];14 return status t::SUCCESS: 15 · ):

## $\underset{^{2} New Features}{\textbf{Knowledge Transfer}}$

#### • Teaching MIPP

- Polytech Sorbonne Engineering School  $-3^{rd}$  year

- Électronique et Informatique Systèmes Embarqués

- Sorbonne University Master 2 SESI

- o Systèmes Électroniques et Systèmes Informatiques

#### Knowledge Transfer <sup>2</sup> New Features

#### • Teaching MIPP

- Polytech Sorbonne Engineering School  $-3^{rd}$  year

- Électronique et Informatique Systèmes Embarqués

- Sorbonne University Master 2 SESI

- o Systèmes Électroniques et Systèmes Informatiques

#### • Teaching AFF3CT

- Sorbonne University SESI M2

- Motion detection and tracking on embedded systems

#### Knowledge Transfer <sup>2</sup> New Features

#### • Teaching MIPP

- Polytech Sorbonne Engineering School  $-3^{rd}$  year

- Électronique et Informatique Systèmes Embarqués

- Sorbonne University Master 2 SESI

- o Systèmes Électroniques et Systèmes Informatiques

#### • Teaching AFF3CT

- Sorbonne University SESI M2

- Motion detection and tracking on embedded systems

- Materials available online for the community

- https://lip6.fr/adrien.cassagne/#teaching

#### Knowledge Transfer <sup>2</sup> New Features

#### • Teaching MIPP

- Polytech Sorbonne Engineering School  $-3^{rd}$  year

- Électronique et Informatique Systèmes Embarqués

- Sorbonne University Master 2 SESI

- o Systèmes Électroniques et Systèmes Informatiques

#### • Teaching AFF3CT

- Sorbonne University SESI M2

- Motion detection and tracking on embedded systems

- Materials available online for the community

- https://lip6.fr/adrien.cassagne/#teaching

- New AFF3CT-core developer documentation

- https://aff3ct.github.io/aff3ct-core/

Gas.1 s.threads;

te number of threads that are executing the sequence.

## $\underset{{}^{3} \text{ Roadmap}}{\text{Table of Contents}}$

▶ Introduction

▶ New Features

▶ Roadmap

► Conclusion

### Job Offer & New Recruit

- Job offer: Inria-DGA convention

- Engineer or post-doc (18 months)

- Mission 1: Improve the DSEL for high level languages

- Mission 2: Use julia to wrap AFF3CT-core and to enrich the library

### Job Offer & New Recruit

- Job offer: Inria-DGA convention

- Engineer or post-doc (18 months)

- Mission 1: Improve the DSEL for high level languages

- Mission 2: Use julia to wrap AFF3CT-core and to enrich the library

- New Recruit: Maxime MILLET

- -- PhD in computer science @ LIP6

- Low level optimizations for SoCs

- SIMD for embedded architectures

- Heterogeneous CPU/GPU implementations

- Optical flow and meteor detection

- DSEL for streaming applications

- Multi-threaded runtime (pipeline & replications)

- DSEL for streaming applications

- Multi-threaded runtime (pipeline & replications)

- Benefit from julia in AFF3CT-core

- High level language with high expressiveness

- Simple type templatization

- Just in Time compilation

- $\circ~$  LLVM passes to simplify AFF3CT-core

- DSEL for streaming applications

- Multi-threaded runtime (pipeline & replications)

- Benefit from julia in AFF3CT-core

- High level language with high expressiveness

- Simple type templatization

- Just in Time compilation

- $\circ~$  LLVM passes to simplify AFF3CT-core

- Study code vectorization in julia

- Compare explicit SIMD.jl versus MIPP

- Are there some limitations?

## AFF3CT-core × julia

- DSEL for streaming applications

- Multi-threaded runtime (pipeline & replications)

- Benefit from julia in AFF3CT-core

- High level language with high expressiveness

- Simple type templatization

- Just in Time compilation

- $\circ~$  LLVM passes to simplify AFF3CT-core

- Study code vectorization in julia

- Compare explicit SIMD.jl versus MIPP

- Are there some limitations?

- Enrich AFF3CT library from code written in julia

- Objective: Simplify the AFF3CT contribution process

- Is it possible to use it in C++ and/or in Python?

## $\underset{{}^{3} \operatorname{Roadmap}}{\operatorname{AFF3CT-core}} - \operatorname{Heterogeneous} \operatorname{Tasks} \operatorname{Support}$

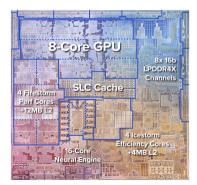

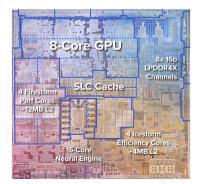

"Nowadays, processor manufacturers are releasing heterogeneous SoCs. On a same chip, we can find: energy efficient cores, performance cores, global memory and application specific accelerators like GPUs & NPUs."

# $\underset{{}^{3} \operatorname{Roadmap}}{\operatorname{AFF3CT-core}} - \operatorname{Heterogeneous} \operatorname{Tasks} \operatorname{Support}$

"Nowadays, processor manufacturers are releasing heterogeneous SoCs. On a same chip, we can find: energy efficient cores, performance cores, global memory and application specific accelerators like GPUs & NPUs."

- All these processing units **share the global memory**

- Take advantage of accelerators without extra copies

- → New optimization opportunities for streaming applications

# $\underset{{}^{3} \operatorname{Roadmap}}{\operatorname{AFF3CT-core}} - \operatorname{Heterogeneous} \operatorname{Tasks} \operatorname{Support}$

"Nowadays, processor manufacturers are releasing heterogeneous SoCs. On a same chip, we can find: energy efficient cores, performance cores, global memory and application specific accelerators like GPUs & NPUs."

• All these processing units **share the global memory**

- Take advantage of accelerators without extra copies

- → New optimization opportunities for streaming applications

- Add heterogeneous tasks support in AFF3CT-core

- Challenges: Enrich DSEL, memory allocations, scheduling

- Possible in julia : CUDA.jl, oneAPI, Apple GPUs

- → Master 2 internship starting February'24 (co-supervised with Julien SOPENA)

### Table of Contents

▶ Introduction

▶ New Features

▶ Roadmap

#### $\blacktriangleright$ Conclusion

- New features

- MIPP: Unsigned integers, SVE support, working on a generator

- AFF3CT-core: Forward sockets, control flow in pipeline stages

- Roadmap

- Wrap & enrich AFF3CT with julia language

- Heterogeneous tasks support in the runtime

### Thank you for listening! Do you have any questions?

<u></u>

- A. Cassagne, O. Hartmann, M. Léonardon, K. He, C. Leroux, R. Tajan, O. Aumage, D. Barthou, T. Tonnellier, V. Pignoly, B. Le Gal, and C. Jégo. "AFF3CT: A Fast Forward Error Correction Toolbox!" In: *Elsevier SoftwareX* 10 (Oct. 2019), p. 100345. DOI: 10.1016/j.softx.2019.100345.

- [2] A. Cassagne, R. Tajan, O. Aumage, D. Barthou, C. Leroux, and C. Jégo. "A DSEL for High Throughput and Low Latency Software-Defined Radio on Multicore CPUs". In: Wiley Concurrency and Computation: Practice and Experience (CCPE) 35.23 (July 2023), e7820. DOI: 10.1002/cpe.7820.

- [3] A. Cassagne, O. Aumage, D. Barthou, C. Leroux, and C. Jégo. "MIPP: A Portable C++ SIMD Wrapper and its use for Error Correction Coding in 5G Standard". In: Workshop on Programming Models for SIMD/Vector Processing (WPMVP). Vösendorf/Wien, Austria: ACM, Feb. 2018. DOI: 10.1145/3178433.3178435.